Chapter 2 操作系统的硬件基础

2.1 计算机三总线硬件结构

计算机硬件结构主要包括CPU、内存和外设。三者通过地址总线、数据总线、控制总线3条总线进行连接。外设需要有IO接口的模块才能连接到总线上。

2.2 CPU结构

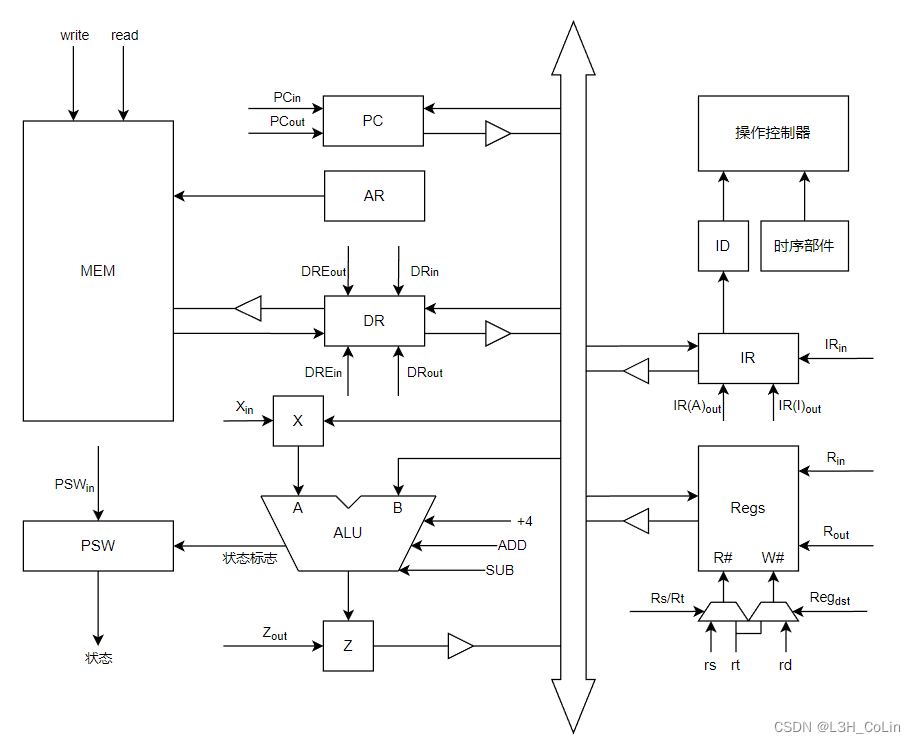

CPU的主要功能是按照一定的逻辑流程分析和执行指令流。CPU在逻辑上可以被划分为3个部分:

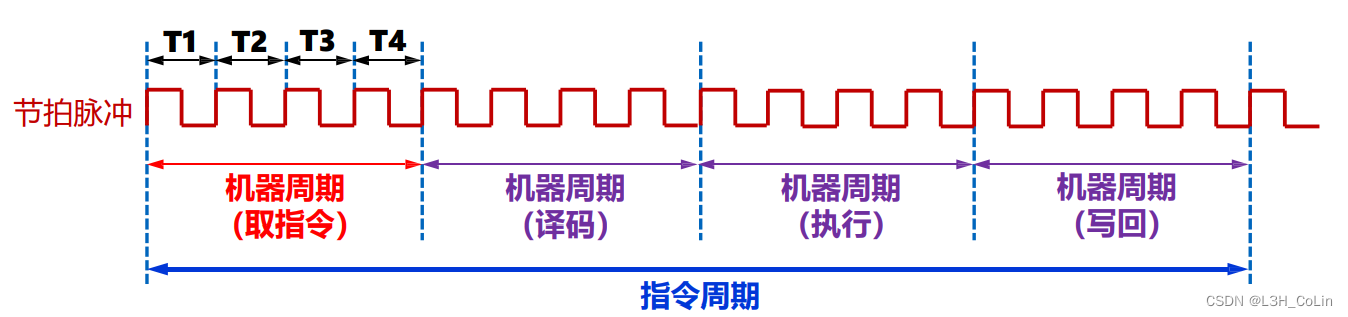

- 控制单元:由指令寄存器、指令解码器、指令计数器等构成。根据用户事先编写好的程序,依次从存储器中取出每一条指令放在指令寄存器中,通过指令解码器分析确定好应该执行什么样的操作,然后按照确定的时序向相应的部件发出微操作控制信号,并更新指令计数器的地址。

- 运算单元:执行算术运算和逻辑运算。接受控制单元的命令而进行动作。

- 寄存器单元:主要指寄存器组,即CPU中暂存数据的地方,保存等待处理的数据或已经处理过的数据。寄存器起到一个缓存的作用,可以减少CPU访问内存的次数,提高其工作速度。寄存器分为通用寄存器和专用寄存器,通用寄存器数量因处理器而异。

2.3 CPU的态

CPU不同的态支持不同的指令集和资源:

- 核态:具有最高特权级,也称为特权态、系统态、内核态或核心态。可以执行所有包括特权级指令,使用所有资源,且能够改变处理器状态。

- 用户态:具有较低特权级,不能使用特权指令,不能直接使用系统资源,不能改变CPU工作状态,只能访问用户程序的存储空间。

- 管态:一个模棱两可的中间状态,介于上面两个状态之间,也可以理解为核态。

特权指令包括:能够改变CPU状态的指令、能够修改特殊寄存器的指令、涉及外部设备的输入输出指令。

硬件按“态”区分CPU的状态,操作系统通过“态”区分进程的状态。

特权级:Intel架构的CPU支持4个特权级,即0-3级,0级最高3级最低。对于一段连续内存(称为段),其头部有段描述符明确规定这段内存的访问特权级,称为描述符特权级(DPL)。UNIX和Linux只支持0、1、3特权级,其中1为管态,Windows只支持0、3级。

CPU的态从用户态向内核态进行转换的方法:

- 系统调用:用户态进程通过系统调用申请使用操作系统提供的服务完成工作。

- 异常:CPU运行时发现不可预知的异常,使当前进程被切换到处理该异常的内核相关程序中。

- 外部设备中断:外部设备发送数据或接收数据就绪后向CPU发出中断信号,CPU暂停执行原来的指令转而去执行与中断信号相关的处理程序。

内核态向用户态转换一般都是IRET的中断返回指令完成的。

2.4 内存

内存又称为主存储器,是计算机系统存放指令和数据的存储器单元。通常分为只读存储器(ROM)、随机存储器(RAM)和高速缓存存储器(Cache)3种类型。

按照与CPU的联系可以分为主存和辅存,主存可以直接与CPU交换信息而辅存不行。

按照存储元的材料可以分为半导体存储器(常用主存)、磁存储器(磁盘等)、光存储器(光盘等)

按照读写工作方式可以分为RAM和ROM。

高速缓存位于CPU和内存之间,容量比内存小但存取速度比内存快,其为内存中一小部分数据的复制,这一小部分数据可能是CPU短时间内访问较为频繁的,CPU访问高速缓存中有的数据时可以减少内存的访问次数,提高CPU速度。

理想的存储系统速度快、容量大、成本低,但现实中不可能实现。现实中将存储系统分层管理,最上层为寄存器,速度最快,容量最小,价格最贵,往下依次为高速缓存、内存、辅存,速度依次降低,容量依次增加,价格依次降低。

CPU访问指令或数据时的访问顺序:

- 访问缓存命中为HIT

- 访问内存命中为MISS

- 访问辅存命中为缺页(PAGE FAULT)

2.6 中断系统

中断是指CPU收到外部信号后停止当前工作,自动转去调用事先准备好的中断服务程序处理外部事件,待处理完毕后再回到原来的中断处继续工作的过程或机制。

引入中断的目的是实现并发活动、实现实时处理、故障自动处理。

引起中断的程序被称为中断源

中断类型可分为:

- 强迫中断和自愿中断,强迫中断是程序没有预期地进行中断,如外部中断;而自愿中断是程序有预期地中断,如访管指令

- 外中断和内中断:外中断由CPU外部事件引起,内中断由CPU内部事件引起。

- 可屏蔽中断和不可屏蔽中断:二者均属于外部中断,不可屏蔽的中断是CPU必须进行响应的,可屏蔽中断CPU可以不响应。

程序中断的地方被称为断点,也即为将要执行的下一条指令的地址。

程序正确运行依赖的信息集合被称为现场,在进入中断程序之前需要进行现场保护,即将CPU的重要信息暂时保存到栈上,中断程序结束后需要恢复现场,即将栈中的CPU信息加载到CPU中。

中断流程:识别中断源→保护断点→保护现场→进入中断服务程序→恢复现场→中断返回。

触发中断使用INT指令实现,从中断返回使用IRET指令实现。

中断响应的实质是交换指令执行地址、交换CPU的态。

2.7 基本输入输出系统

BIOS,固化到计算机中的一类程序,是计算机加电后运行的第一个软件,为计算机提供最初级的最直接的硬件操控。

- 加电自检及初始化:加电自检(POST)用于计算机刚接通电源时对硬件部分的检测,通常是对CPU、内存等进行测试。发现问题会直接警告。然后会查找其他设备的BIOS并执行这些设备的BIOS。

- 设置CMOS参数:用于帮助用户设置基本的系统参数,如系统日期等。

- 系统启动:根据用户指定顺序从硬盘或光驱等媒介启动操作系统,为用户建立用户环境,OS启动后就由OS接管计算机。

- 基本输入输出处理程序:为应用程序和操作系统提供硬件接口服务,这些服务主要与输入输出设备有关,如键盘操作等。BIOS使用的基本中断号为10H-1FH,如13H表示软盘调用,INT 13标号为02的子功能为读扇区。

系统BIOS的位置为F0000H-FFFFFH。

2.8 操作系统启动过程

2.8.1 操作系统启动概述

实模式:程序按照8086方式进行寻址,寻址位一共20位,共可以访问1MB的地址空间,由CPU单任务进行。实模式前640KB(00000H-9FFFFH)为基本内存,中128KB(A0000H-BFFFFH)为显卡显存,后256KB(C0000H-FFFFFH)为BIOS系统。

保护模式:内存保护模式,地址寻址共32位,可寻址4GB空间。在该模式下段具有了新的含义和工作机制,且新增了多个寄存器可以操作。其中的地址均为虚拟地址,应用程序和操作系统的运行均被保护。此时CPU支持多任务。

操作系统的启动过程:

- 初始引导:用于将OS内核加载到内存的指定位置,从BIOS的启动代码开始执行开始。按下电源开关后电源开始供电,控制芯片组让CPU恢复到初始状态。之后CPU开始执行FFFF0处的代码,BIOS开始进行加电自检。自检完成后开始运行BIOS启动代码,主要用于寻找可用的启动设备,并将其中的引导程序加载到内存中。引导程序可以加载操作系统到内存中的适当位置,并将CPU使用权交给OS内核。

- 核心初始化:用于OS内核初始化系统的核心数据,并继续加载操作系统除了内核之外的部分到内存中。该过程还包含初始化存储系统和页表、构建核心进程、引导内核运行等,最终控制权将被交给内核,进入系统初始化阶段。

- 系统初始化:继续初始化操作系统,并最终准备好操作系统的桌面和控制台,该过程主要包含初始化文件系统、初始化网格系统、初始化控制台、初始化图形界面,最终处于待命状态。

DOS系统的启动过程:

- POST,BIOS自检。

- 初始引导,BIOS从MBR(主引导记录)中读取引导程序,并加载到内存,引导程序将io.sys和msdos.sys加载到内存中,DOS系统开始运行并接管系统。

- 核心初始化,操作系统读取config.sys配置系统核心。

- 系统初始化,操作系统读入 Command.com,执行autoexec.bat,系统待命。

Windows的启动过程:

- POST,BIOS自检。

- 初始引导,BIOS从MBR(主引导记录)中读取引导程序,并加载到内存,引导程序启动DOS7.0,调入操作系统核心,然后由Windows接管系统。

- 核心初始化

- 系统初始化

2.8.2 Linux启动过程

- POST

- MBR

- KERNEL映像

- KERNEL映像自解压并执行

- 内核初始化

- 内核启动

在内核完成引导后需要加载init程序,init进程是所有进程的祖先,进程号为1。init首先使用/etc/inittab脚本文件进行系统初始化,然后执行一系列文件设置其他选项,最后设置键盘、字体等。

操作系统的安装过程:首先需要将OS映像拷贝到存储空间,后写启动相关代码和数据(MBR中的PBR)。对于多操作系统的安装需要修改MBR,进行重写或追加。

MBR:主引导记录,又称为主启动扇区,是计算机开机后访问硬盘必须访问的第一个扇区,操作系统启动相关数据和代码就保存在主启动扇区中。大小为512字节,最后两个字节为0x55和0xAA表明该设备可以用于启动。主引导记录中主要包含有磁盘分区信息、启动参数、操作系统内核位置信息、引导代码等。

2.10 操作系统的生成

一些操作系统可以根据用户需要进行配置和构建。其前提是:

- 由可以拆装的模块生成

- 有交互式配置工具

- 有映像构建工具

对于Linux系统即可以通过下载内核、选择和启动配置程序进行配置内核模块和参数、编译新的内核、安装和启动内核这些步骤来完成操作系统的生成。